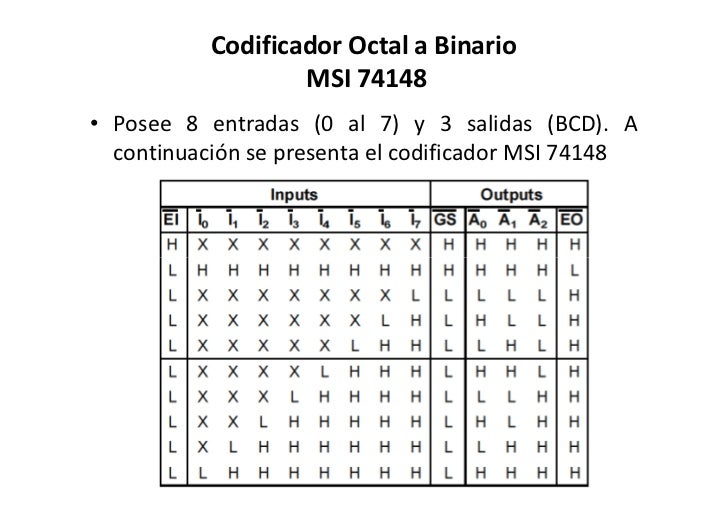

El circuito 74LS148 es un codificador que realiza una codificacion de varias entradas, en unicamente un maximo de 3 digitos con una salida de forma binaria, dependiendo el pin de entrada en ALTO o en BAJO.

Descripción del codificador 74LS148

El 74LS148 es un codificador de prioridad de 8 a 3 líneas con características de descodificación de prioridad de las entradas para garantizar que solo se codifique la línea de datos de mayor orden.

El 74LS148 codifica ocho líneas de datos para BCD de tres líneas (4-2-1). La condición implícita de cero decimal no requiere ninguna condición de entrada ya que el cero está codificado cuando las ocho líneas de datos están en un nivel lógico alto. Se ha proporcionado un circuito en cascada (entrada habilitada E1 y habilite la salida E0) para permitir la expansión octal sin la necesidad de circuitos externos. Para todos los tipos, las entradas y salidas de datos están activas en el nivel lógico bajo.

En la siguiente tabla de la verdad se muestra las salidas dependiendo de los valores en las entradas.

| Familia | LS |

| Tensión de alimentación mínima | 4.5 V |

| Tensión de alimentación máxima | 5.5 V |

| Corriente de salida baja | 0.4 mA |

| Corriente de salida alta | 4 mA |

| Disipación de potencia | 225 mW |

| Retardo de propagación | 10 ns |

| Temperatura de funcionamiento mínima | 0°C |

| Temperatura de funcionamiento máximo | 70°C |

| Característica | |

|---|---|

| Largo | 0 cm |

| Ancho | 0 cm |

| Alto | 0 cm |

| Peso | 0 gr |