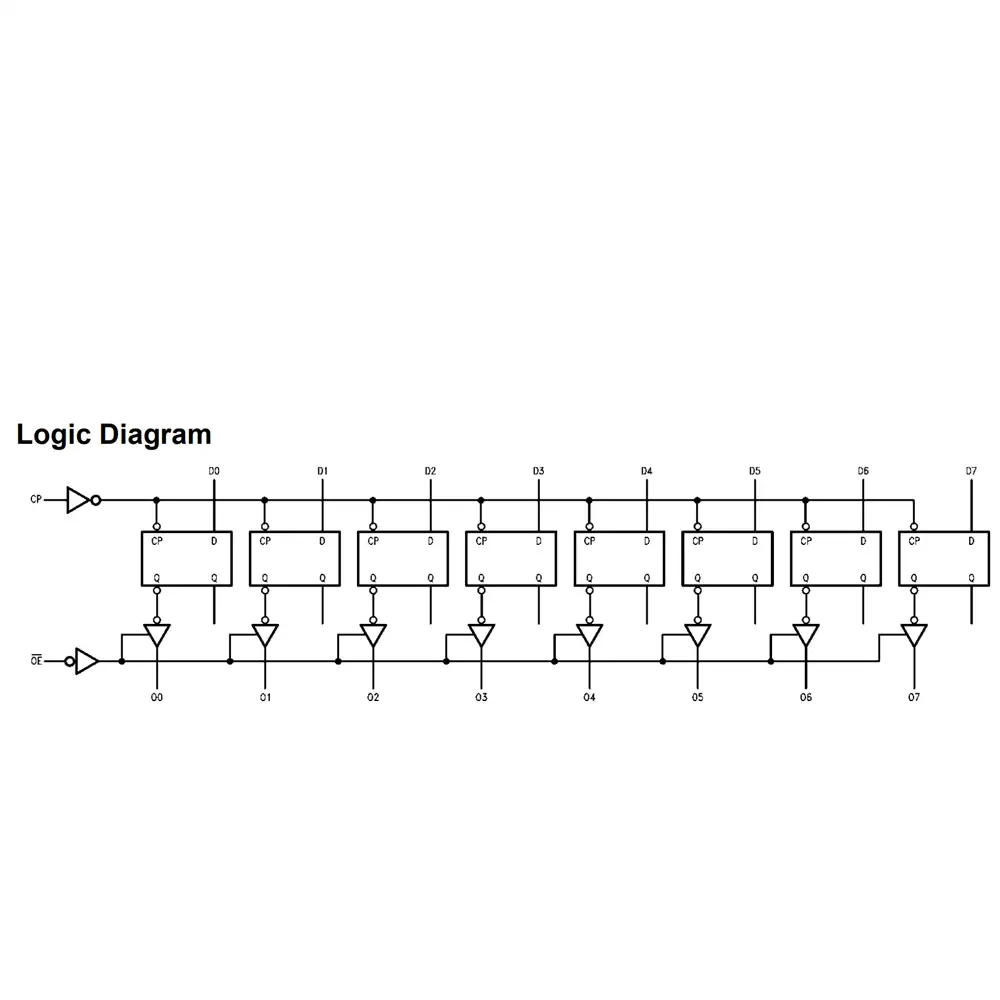

El DM74LS574 es un flip-flop octal de alta velocidad y baja potencia. con un reloj común protegido (CP) y una salida de habilitación común protegida (OE).

Flip-Flop tipo D

El flip-flop tipo D, sigue a la entrada, haciendo transiciones que coinciden con las de la entrada. El término D, significa dato; este flip-flop almacena el valor que está en la línea de datos. Se puede considerar como una celda básica de memoria. Un flip-flop D, se puede hacer con un flip-flop "set/reset", uniendo la salida set (estado alto) con la salida reset (estado bajo), a través de un inversor. El resultado se puede sincronizar.

Un problema con el flip-flop set-reset con compuertas NAND con entrada de control es que puede haber una salida no valida cuando las entradas set y reset son ambas 1. Éste es el estado no utilizado y debe evitarse en lo posible. Para evitar esto se coloca un inversor entre las entradas set y reset. Esto crea una nueva entrada que se llamará D.

Salida del Flip-Flop tipo D

El flip-flop D intenta seguir a la entrada D, pero no puede hacer la transición requerida a menos que esté habilitado por el "clock" (pulso de sincronismo). Nótese que si el clock es low (está bajo) cuando ocurre una transición en D, la transición correspondiente en Q, ocurre a la siguiente transición alta del clock.

| Familia | LS |

| Tipo de Flip-Flop | D |

| Retardo de propagación | 13 ns |

| Frecuencia | 33 MHz |

| Salida de corriente | 8 mA |

| Tensión de alimentación mínima | 4.75 V |

| Tensión de alimentación máxima | 5.25 V |

| Temperatura de funcionamiento mínima | 0°C |

| Temperatura de funcionamiento máximo | 70°C |

| Característica | |

|---|---|

| Largo | 0 cm |

| Ancho | 0 cm |

| Alto | 0 cm |

| Peso | 0 gr |

-

attach_file

0.05 MB datasheet 74LS574 (2020-05-20 01-20-44).pdfcloud_download