Circuito Integrado TTL 74LS112. Flip-flop J-K negativo biestable T con funciones clear y preset Cuando las funciones de preset y clear están inactivos (alto), los datos a las entradas J y K que satisfacen los requisitos de tiempo de configuración se transfieren a las salidas en el borde con pendiente negativa del pulso de reloj. Reloj de activación se produce a un nivel de tensión y no está directamente relacionada con el tiempo de subida del pulso de reloj. Tras el intervalo de tiempo de espera, los datos a las entradas J y K pueden ser cambiados sin afectar los niveles en las salidas. Este versátil flip-flop puede funcionar como conmutador biestable atando J y K alta.

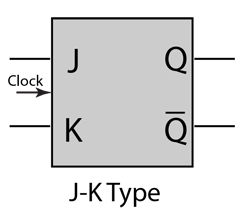

Flip-Flop J-K

El "flip-flop" J-K, es el más versátil de los flip-flops básicos. Tiene el carácter de seguimiento de entrada del flip-flop D sincronizado, pero tiene dos entradas, denominadas tradicionalmente J y K. Si J y K son diferentes, la salida Q toma el valor de J durante la subida del siguiente pulso de sincronismo.

Si J y K son ambos low (bajo), entonces no se produce cambio alguno. Si J y K son ambos high (alto), entonces en la siguiente subida de clock la salida cambiará de estado. Puede realizar las funciones del flip-flop set/reset y tiene la ventaja de que no hay estados ambiguos. Puede actuar también como un flip-flop T para conseguir la acción de permutación en la salida, si se conectan entre sí las entradas J y K. Esta aplicación de permutar el estado, encuentra un uso extensivo en los contadores binarios.

Estructura del Flip-Flop J-K

A la derecha se tiene una versión simplificada del versátil flip-flop J-K. Nótese que las salidas se retroalimentan para habilitar las puertas NAND. Esto es lo que le proporciona la acción de permutación cuando J=K=1.

Si bien esta implementación del flip-flop J-K con cuatro puertas NAND funciona en principio, hay problemas que surgen con el tiempo ("timing"). El pulso de "timing" debe ser muy corto porque un cambio en Q antes de que aquel se apague puede conducir el circuito a una oscilación llamada "carrera". Los circuitos integrados modernos son tan rápidos que esta sencilla versión del flip-flop J-K no es práctica.

| Familia | LS |

| Tipo de Flip-Flop | JK |

| Tipo de disparo | Edge Negativo |

| Tipo de salida | Diferencial / complementaria |

| Retardo de propagación | 15 ns |

| Frecuencia | 30 MHz |

| Tensión de alimentación mínima | 4.75 V |

| Tensión de alimentación máxima | 5.25 V |

| Corriente de salida | 8 mA |

| Temperatura de funcionamiento mínima | 0°C |

| Temperatura de funcionamiento máximo | 70°C |

| Característica | |

|---|---|

| Largo | 0 cm |

| Ancho | 0 cm |

| Alto | 0 cm |

| Peso | 0 gr |

-

attach_file

0.05 MB datasheet 74LS112 (2020-05-19 16-28-43).pdfcloud_download